- Fpga = плис = Программи́руемая логи́ческая интегра́льная схе́ма (на печатной плате)

- Есть Китайские ПЛИС, есть даже Воронежские (для специальных задач)

- ”CPU и FPGA – микросхемы общего применения, туда спецзакладку для сети запихивать накладно, а вот в специализированный сетевой чип, который примерно весь Blackbox со своими закрытыми процами внутри – святое дело)” (c)

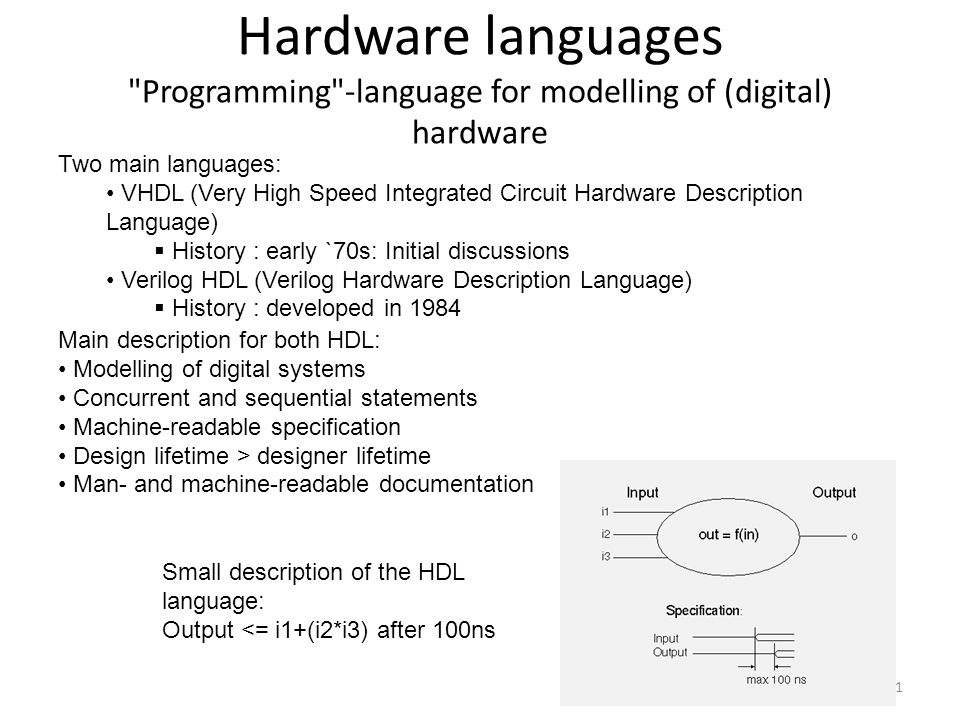

- Язык Verilog/VHDL. Оба они являются HDL – hardware description language. Т.е. языки аппаратного программирования. В целом разработка на Verilog/VHDL считается значительно более долгой в сравнении с ПЯВУ. Разрабатывать FPGA с одной стороны легко т.к. всегда видишь что происходит (на слайде стриминг схема), с другой сложно т.к. сигналов много.

- Плюсы FPGA: Параллельность, предсказуемость, свобода в архитектуре и периферии

- Зачастую для FPGA есть эмуляторы платы FPGA, чтобы ты мог свой код протестировать через эмулятор, без девайса

- Частота 500 МГЦ для FPGA это нормально и даже много. Нужно понимать, что это не процессор. Причем чем сложнее разработанная схема, тем сложнее поддерживать нужную частоту (если сложная логика между элементами например). Аналогично и в ASIC.

- Большая часть FPGA разработки в России и мире это военка (даже язык VHDL был разработан для US DoD – см. Выше), космос, авто – там, где требуется обработка чего то (трафика, видео) с жестко предсказуемой производительностью/задержкой. FPGA позволяет делать без задержек приложения/устройства с гарантией скорости их работы, что важно, например, в автомобильном производстве (automotive). Военка отсюда же вытекает. Так же на марсоходах используется FPGA.

- Производители Altera (Intel)/Xilinx (AMD) (основные).

- Часть блоков кода в проектах зачастую повторяемые (можно скачать/найти/купить).

- В Cisco 6880 есть и ASIC (на интерфейсах) и FPGA (коммутационные матрицы). Можно как баги править, так и функционал добавлять через прошивку FPGA. В целом это достаточно типовая архитектура на сегодня.

- Неплохая статья о разработке FPGA в контекте где пригождается TCL, много особенностей разработки на FPGA не только в контексте TCL (процесс, глюки софта и проч)

- (Linkmeup подкаст FPGA) Зачастую реализации на базе FPGA невозможно положить за счет объема трафика/(D)DoS, потому что они могут обработать line rate трафика без потерь с неизменной задержкой от объема. FPGA, ASIC зачастую круты тем, что решения на чипе делаются еще до того как пакет полностью принят и в момент приема остается это решение только применить. Кроме того буферы входящие/исходящие никак не зависят друг от друга.

- Пример описания Беркута Метротек: FPGA HDL (заложенная ими логика в FPGA – MAC control, генератор, анализатор, передача и прием пакетов), Linux (там пишется аппа которая реализует RFC 2544/Y-1564, интерейсы просмотра и управления). Для Linux пишется прошивка, чтобы FPGA там выглядил как обычный NIC и можно было даже перехватывать с нее данные обычным wireshark/tcpdump.

- Бинарник хранится в постоянной памяти как прошивка для FPGA, далее при загрузке девайса происходит установка значений для блоков в соответствии с прошивкой. Причем в реализации у метротека под каждый тест своя прошивка – отдельная для RFC 2544, отдельная для Y-1564. При смене прошивки девайс перезагружается за пару секунд и способен начинать новый тест. Может быть частичная реконфигурация, тем посложнее – указание конкретных ячеек для переконфигурации, а не всех.

- Таблица с asic/fpga datacenter коммутаторов cisco/arista/juniper/huawei

Network switch comparison Table, including ASIC and packet buffer.

- С точки зрения импортозамещения нет российских FPGA/ASIC. Не полностью доверенные схемы поэтому в любом случае. При этом FPGA со своей/известной логикой (вплоть до проверок ошибок CRC) лучше чем западный ASIC с неизвестной логикой.

- Intel (Altera) Stratix V используют в Беркуте Метротека (тестер/анализатор)

- Крутые FPGA 10/100G – Altera (куплен Intel). Продают dev-kit за 5к баксов для 10G (Arria) и 20к (Stratix).

FPGA Altera

The main product lines from Altera (now Intel) are the Stratix, Arria and Cyclone series FPGAs,[1] the MAX series CPLDs and non-volatile FPGAs,[1] Quartus design software,[6][7] and Enpirion PowerSoC DC-DC power solutions.

Stratix

https://www.intel.com/content/www/us/en/programmable/products/boards_and_kits/all-development-kits.html

https://www.intel.com/content/www/us/en/programmable/products/boards_and_kits/dev-kits/altera/kit-stratix-iv-gt-100g.html

$19,995

https://www.intel.com/content/www/us/en/programmable/products/boards_and_kits/dev-kits/altera/kit-stratix-v-gx-100g.html

$24,995

Arria

https://www.intel.com/content/www/us/en/programmable/products/boards_and_kits/dev-kits/altera/kit-a10-gx-fpga.html

$4,495

- Intel Quartus Prime – Intel Quartus Prime содержит все что вам нужно для разработки дизайна систем на базе Intel FPGA, SoC и Complex Programmable Logic Device (CPLD), начиная с самых основ и включая далее отладку взаимодействия, оптимизацию, верификацию и моделирование.

Создание ASIC

- Те, кто идет по пути создания ASIC, программируют на FPGA плате обычно и только потом в ASIC переливают проверенную реализацию. Но многие разработчики как нишевых (напр. метротек), так и массовых девайсов (включая коммутаторы) не делают ASIC вообще – слишком рискованно, большие инвестиции, трудозатраты и риски неисправляемых багов, отсутствие гибкости по развитию.

- ASIC часто делается в 2-3 захода, не с первого.

- Time-to-market высокий (до нескольких лет – сложность разработки, большие вложения). Но в результате продукт дешевый, по сравнению с FPGA. А FPGA ту же задачу можно решить за неделю-месяц, причем без больших капитальных вложений.

- ASIC вызженно в камне. Цена ошибки огромна, в отличии от FPGA. Миллионы долларов в помойку. Есть миллион и тысяча примеров, когда выпускалась партия сетевушек реализованных на ASIC, где позже находилась мелкая, но очень неприятная бага которую невозможно поправить на уровне драйверов и производитель краснея выпускал новую ревизию устройств, неся серьёзные убытки. Целая индустрия на этом. ТЕСТИРОВАНИЕ мега важно. В случае с FPGA, среднестатистическое исправление ошибок занимает две недели. Или быстрее, если косяк вышел совсем уж неприятный.

- Можно делать как в FPGA все что хочешь, но зависит от бабок (если у тебя такой большой заказ что фабрика чисто под тебя будет печатать)

- Код пишется, потом преобразуется в фикс-конфигурацию из транзисторов, потом ты тестируешь реализацию. Альтернативный подход (бюджетнее) – конвертация фиксированной конфигурации FPGA в ASIC, но производительность может быть хуже.

SoC

Сейчас Метротековцы активно работают с относительно новой платформой — SoC (System on Chip). Смысл SoC — размещение функциональности полноценной системы в одном чипе. Например, можно объединить ARM, FPGA и кусочек памяти под одной крышей. Это даст огромную скорость внутренней коммуникации в рамках одного кристалла, освободив от узких мест в виде разнообразных шин передачи данных. Скорость зависит от кристалла, но обработка данных на скорости 560 Гбит/с совершенно реальные цифры.

FPGA + Python

Из песочницы

Технология FPGA (ПЛИС) в настоящее время обретает большую популярность. Растёт количество сфер применения: помимо обработки цифровых сигналов, FPGA используются для ускорения машинного обучения, в blockchain технологиях, обработке видео и в IoT.

Данная технология имеет один существенный минус: для программирования используются довольно старые и специфичные языки описания цифровой аппаратуры Verilog и VHDL. Это осложняет вхождение новичка в FPGA и для работодателя найти специалиста с этими специфичными знаниями на рынке труда сложно. С другой стороны популярный высокоуровневый язык программирования Python с фреймворком MyHDL делают программирование FPGA простым и приятным. Тем более людей знающих Python на порядок больше специалистов владеющих Verilog/VHDL. Серией статей я хочу показать как легко и просто войти в область FPGA зная Python и начать делать настоящие сложные FPGA проекты на этом языке.